# An Improvised Quality Aware Adaptive Aware Routing for on chip based Wireless Network on Chip Communication

B.Nageshwar Rao and N.S.Murti Sarma

<sup>1</sup>(Research Scholar, department of ECE, Rayalaseema University, Kurnool, Andhra Pradesh, Indi <sup>2</sup>(Professor Sreenidhi Institute of Science and Technology, Yamnampet, Ghatakesar, Hyderabad, India.) Corresponding Author: B.Nageshwar Rao

**Abstract:** Adaptive on-chip verbal exchange is crucial to the layout of multi-center System-on-chip. Wormhole routers offer an powerful mechanism to alternate information a number of the more than one cores inside the NoC. Efficient packet allocation can improve the performance of adaptive wormhole routing with the aid of prioritizing uncongested packets to reach their destinations first. This paper gives a routing method that collects site visitors/congestion data, and employs it to prioritize lengthy distance visiting packets throughout excessive congestion. Each NoC router collects site visitors/congestion statistics from its close by routers and makes routing decisions to pick some packets for visiting first that could attain their destination cores quicker. We make use of header flits to hold congestion records in place of including devoted verbal exchange links a few of the routers. It saves more conversation hyperlinks among routers, and less difficult SoC format is performed due to fewer interconnection wires. Our NoC router layout improves the NoC throughput. The experimental effects suggest performance development for long distance traffic.

Keywords: Low Power, Network on Chip, Bufferless, Bottleneck Algorithm.

| Date of Submission: 28-08-2017 | Date of acceptance: 08-09-2017 |

|--------------------------------|--------------------------------|

## I. Introduction

Multi-center SoCs (System-on-a-Chip) have advanced with new on-chip applications. Processing, reminiscence and other IP cores require higher on-chip verbal exchange bandwidth, which traditional busprimarily based SoCs can not provide. Community-on-chip (NoC) has higher bandwidth and permits simpler growth of multi-middle structures. But, NoCs can't manage massive scale information transfers and efforts are being made to reduce congestion to increase the general throughput of the NoC structures. Congestion in the NoC can be stepped forward by way of decreasing the latency. Generally, NoCs hire digital channel (VC) based totally wormhole routing. The usage of dynamic buffering permits every character VC to growth its buffer size to deal with the ultimate flits of a packet to lessen blockading [1]. However, dynamic buffering primarily based VCs have their personal issues including complexity, intervention among VCs, and so forth. Early adaptive routers made their packet routing decisions based totally at the traffic records in their pals [2]. An preliminary adaptive NoC router switches to adaptive routing for a site visitors congestion threshold. There are many advantages of adaptive routing in comparison to deterministic (e.G. XY) routing. But, in comparison to pure deterministic routing including DOR (dimension Order Routing), adaptive routing can result in deadlocks. The peculiar-Even turn version has been proposed as one of the answers for deadlock and stay lock free adaptive routing [2]. The adaptive routing proposed by using Kim et al. Employs course mapped VCs to prevent deadlocks [3]. In direction mapped VC allocation, each VC is mapped to an output path that routinely removes any cyclic routing patterns. Break out VC changed into proposed by way of Duato as an trade to prevent impasse [4]. A particular get away VC is precise for usage to attain impasse loose routing. Making use of a sideband community for the transmission of congestion facts has been proposed by using unique researchers [5– 7]. Gratz et al. Proposed regional Congestion cognizance (RCA) methodology, that considers the congestion past the direct associates to improve throughput [5]. It is also argued that vacation spot based totally adaptive routing algorithms (DAR and DBAR) carry out better than local adaptive routing strategies [6, 7]. The architectures proposed use a sideband network. Adaptive routing can be similarly advanced by utilising a worldwide Congestion attention (GCA) mechanism [8]. We gift a congestion conscious NoC router that gives better overall performance in the course of congestion at the same time as operating at close to saturation traffic situations.

#### **II.** Overview And Motivation

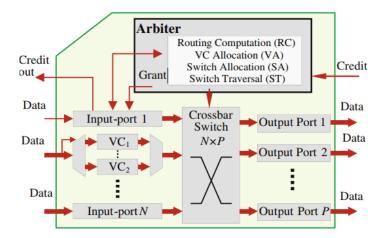

An ordinary wormhole NoC router is shown in Fig. 1. The micro-architecture of a conventional router consists of enter and output ports, an arbiter, and a crossbar transfer. In this paper, the input-ports include the VC buffers, and the output-ports are easy records buses. After buffering a flit, the enter-port issues a request signal to the arbiter. The arbiter contains VC and transfer allocators and performs arbitration some of the potential VC flits that make request to access the crossbar and different shared sources [9]. The crossbar switch can be configured to connect any enter buffer of the router to any output port, in which one enter-port is attached to simplest one output-port.

Fig. 1. Typical wormhole NoC router

Destination-primarily based congestion-aware adaptive routing improves latency within the NoC for excessive traffic situations. Most of the local congestion aware based NoC routing research is focused on enhancing the latency and throughput through refining the routing mechanism. The baseline NoC routers use round-robin (RR) scheme for each VC and switch allocation because of its simplicity. There are numerous blessings of the usage of the round-robin VC and transfer allocation; however, this scheme isn't green in extraordinary site visitors eventualities. Organisation of packets in a selected order will genuinely allocate a packet to a congested VC and the packet might not be able to tour in the NoC effectively. For confined quantity of VCs, allocating an trade packet that has no congestion on its direction will enhance the general NoC latency and throughput. One of the approaches to present overall performance of on-chip communication community is latency, which is the time taken through a packet to reach its vacation spot. There are specially two categories of latency that can be measured for various traffic patterns. Common latency is commonly used to assess the overall performance of the NoC. However, for common latency, some packets experiencing high latency can be hidden. Maximum latency represents the worst-case state of affairs, in which a packet could revel in the highest latency. Typically packets that travel between the routers/cores positioned on the opposite ends of a second-mesh NoC suffer the worst latencies.

## 2.1.Congestion Aware NoC Routing

In congested NoCs, a packet can spend most of its time looking ahead to a VC venture that is a buffer slot within the downstream router. The ready time for a packet traveling lengthy distance from the current router to its destination will not growth drastically if that packet is held in-among until the comfort of congestion. The gain of allocating available VCs to any other packet with decrease delays to its destination will allow that packet to traverse the NoC quickly. A few applications have site visitors patterns, which normally varies with intervals of packet burst. In an unsaturated NoC, energetic packets going through delays (due to congestion) in accomplishing their destinations will wait till the comfort of congestion earlier than persevering with their journey within the NoC. Local adaptive routing algorithms together with RCA, DAR, DBAR and GCA utilize congestion information all through the routing decision making manner [5-8]. Further to utilising the congestion records for adaptive routing, we advocate to apply the statistics for VC allocation to enhance performance. In location of RR-based VC allocation, we gift a Quality -aware VC allocator to prioritize uncongested VCs to allocate them first. It is especially useful while simplest a constrained range of VCs are to be had. In addition to prioritizing the allocation by means of the VC allocator, a comparable technique is implemented to the switch allocator. Thinking about that sure packets could take longer to reach their destinations, prioritization may be carried out to packets that would be stuck within the NoC due to congestion. These packets are usually those that travel longer distance throughout the NoC as they have got extra chances to wait as allocation may additionally fail for them. It increases the average latency as those packets are likely to spend vast quantity of time while ready in a congested vicinity of the NoC. The allocation methodology in NoC router is custom designed to improve the performance for all the packets. The technique is improved by using lowering the concern of Congestion aware Routing for On-Chip communication in NoC systems 549 lengthy distance packets beneath congested situations that effects in better NoC latency. There are two processes to regulate round-robin arbitration i.E. Either by changing how VCs are allocated or how flits are allotted by way of the transfer allocator.

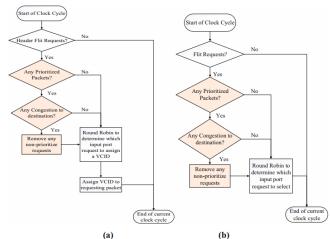

# 2.2.VC/Switch Allocation

VC allocation is a vital technique wherein the arrival packets are assigned a VC identity (VCID) within the downstream router. Fairness and impasse avoidance are taken into consideration throughout this system. We propose to amend the RR-based totally allocation to make certain that no packets are starved while improving the latency and throughput of the NoC. With the destination-primarily based adaptive routing, congestion is determined for the current source to the vacation spot router. Using the congestion records, a changed roundrobin technique will deny any VC allocation requests if a packet direction to the destination is greater than a threshold (range of hops). For an NxN mesh NoC, we use a threshold of N\*3/2 in this paper. If congestion persists for that packet, it's also critical to avoid starvation. A counter sign up is used to music the wide variety of cycles that the packet is hung on waiting. While the counter reaches to a maximum allowed wait time, the packet is treated as uncongested and might be allocated in a round-robin manner. Parent 2a illustrates our proposed VC allocation mechanism. Switch allocation is a system in which flits are decided on for crossbar traversal at every clock cycle. Underneath everyday instances, RR-based totally method accepts request of simplest one VC at a time and then prioritizes it for the following VC request. To improve average latency for prioritized lengthy distance packets, the scheme is changed to allow those packets to permit two flits to be allocated in consecutive cycles earlier than allowing the round-robin counter to increment for the following VC. The amended transfer allocation process is given in Fig. 2b. Packets have a prioritization flag to indicate that the packet can be prioritized. It's miles essential to limit the wide variety of packets being prioritized to avoid nonprioritized packets from ravenous. Usually for a 2nd-mesh NoC, only packets touring longer distances (i.E. Packets travelling from one nook to another) are prioritized. Our Quality aware adaptive routing (QAAR) can be prolonged for QoS programs wherein sure packets are given priority to ensure lower latency. Our VC allocation manner of Fig. 2a, determines if the QAAR mechanism will prioritize any VC allocation requests or now not. While an unassigned packet requests for an output VCID and it is prioritized, QAAR would ignore (based totally on congestion facts) the non-prioritized requests and carry out allocation between prioritized requests.

# 2.3.Congestion Aware Adaptive Router Micro-Architecture

Further to the NoC router additives shown in Fig. 1, QAAR router has a header extractor, congestion awareness element, (enter) port pre-selection and header substitute additives at the output-ports as shown in Fig. Three. Moreover, QAAR router also employs congestion focus prioritization for VC (CVA) and switch arbitration (CSA). CVA mechanism given in Fig. 2a handiest prioritizes VC allocation while CSA simplest prioritizes the transfer allocation following the CSA mechanism illustrated in Fig. 2b. The proposed QAAR router micro-structure is a pipelined adaptive NoC router based totally on the baseline adaptive router [3]. The router includes five degrees: Buffer Write (BW), direction Computation (RC), VC allocation (VA), transfer Allocation (SA) and Crossbar Traversal (XT).

Fig. 2. (a) CVA: Quality-aware VC allocation (b) CSA: Congestion-aware switch allocation

Furthermore, one cycle is needed for channel hyperlink Traversal (LT). Look-ahead routing is leveraged to allow the router output guidelines that can be pre-selected to take away the BW level from the pipeline. A flit that arrives at the router will traverse the allocators without delay in parallel to buffering if the flit fails to win an output port. Speculative transfer allocation is applied to permit each VA and SA tiers to proceed in parallel. In our proposed QAAR router, the quantity of available VCs is used as a congestion evaluation metric. Ma and others have hired unmarried-bit information to symbolize the congestion kingdom of unique router referred to as DBAR [7]. Based totally on the identical concept, every router propagates congestion information to its neighboring (specially upstream) routers. We embed the congestion facts inside the header flits rather than a sideband community used in DAR [6] and DBAR [7]. Our technique is an prolonged model of RCA mechanism [5]. The lately proposed NoCs have 128-bit size flits with many unused bits in the header flit. The congestion statistics could require at least 1-bit consistent with router or 8-sixteen bits in general for an eight 8 mesh topology NoC. We make use of a vacation spot primarily based congestion table to track traffic conditions, which is much like DAR and DBAR techniques. The congestion table is up to date as new congestion facts will become to be had. The routing computation would utilize this desk to make decisions for adaptive routing.

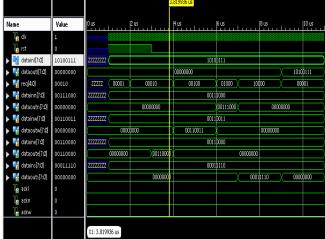

Fig (3) Simulation Results of Proposed Buffer less NoC Design

The proposed scheme was implemented and simulated using the Xilinx 14.2 tool and results achieved clearly showing that the overall power was reduced when compare to the conventional Network on Chip Architecture and also the proposed Buffer less NoC based Architecture having the best Power Efficiency ratio against the all possible at stages in communication processors.

| Device Utilization Summary (estimated values) |      |           |             |

|-----------------------------------------------|------|-----------|-------------|

| Logic Utilization                             | Used | Available | Utilization |

| Number of Slices                              | 1329 | 23872     | 5%          |

| Number of Slice Flip Flops                    | 157  | 47744     | 3%          |

| Number of 4 input LUTs                        | 1065 | i 47744   | 2%          |

| Number of bonded IOBs                         | 92   | 469       | 19%         |

| Number of GCLKs                               |      | . 24      | 4%          |

The following figure (4) shows the overall Area utilized by the proposed Buffer less logic based NoC cores.. These results showing that the overall Area utilized by the proposed NoC was having very low area when compare to the existing systems.

| Method                 | Frequency(MHz) | Dynamic Power (mW) |

|------------------------|----------------|--------------------|

| Proposed Scheme        | 1GHz           | 11                 |

| Conventional Scheme[1] | 1GHz           | 30.96              |

And the below figure(5) shows that the overall power usage of the proposed Buffers less NoC with novel bottleneck algorithm based router. These results shows that power dissipation of the proposed scheme was 0.011W that is extremely reduced compare to previous conventional schemes.

#### **IV.** Conclusion

This paper affords a novel method to enhance NoC latency and throughput by packet prioritization. The goal is to lessen NoC latency and improve NoC throughput by way of the use of congestion data. Our adaptive routing employs nearby congestion to enhance packet routing in high visitors NoCs. We've got extended the local congestion focus records to different parts of the router, usually to the arbiters to enhance packet choice for both VC and transfer allocators. A brand new methodology of Quality aware Adaptive Routing (QAAR) is designed to prioritize the allocation of packets that suffer higher latency at the same time as journeying long distances between source and vacation spot cores. QAAR additionally eliminates the sideband community to transfer congestion facts. QAAR technique indicates tremendous overall performance improvement.

#### References

- Nicopoulos, C., Park, D., Kim, J., Vijaykrishnam, N., Yousif, M.S., Das, C.R.: ViChaR: a dynamic virtual channel regulator for [1]. Network-on-Chip router. In: Proceedings of the International Symposium on Microarchitecture, pp. 333-344 (2006)

- [2]. Hu, J., Marculescu, R.: DyAD-Smart routing for Network-on-Chip. In: Proceedings of the Design Automation Conference, San Diego, CA, pp. 260-263, July 2004

- Kim, J., Park, D., Vijaykrishnam, N., Das, C.R.: A low latency router supporting adaptivity for on-chip interconnects. In: [3]. Proceedings of the Design Automation Conference, pp. 559-564, June 2005

- [4]. Duato, J.: A new theory of deadlock-free adaptive routing in wormhole networks. IEEE Trans. Parallel Distributive Syst. 4(12), 1320-1331 (1993)

- [5]. Gratz, P., Grot, B., Keckler, S.W.: Regional congestion awareness for load balance in Network-on-Chip. In: Proceedings of the IEEE International Symposium on High Performance Computer Architecture, Salt Lake City, pp. 203-214, April 2008

- John Jose, Bhawna Nayak, Kranthi Kumar, Madhu Mutyam, "DeBAR: Deflection based adaptive router with minimal buffering", in DesignAutomation and Test in Europe Conference, pp.1583-1588, March 2013. [6].

- Jing Lin, Xiaola Lin, Liang Tang, "Making-a-stop: A new bufferless routing algorithm for on-chip network", *Elsevier Publish Journal ofParallel and Distributed Computing*, pp.515-524, 2012. [7].

- Chris Fallin, Greg Nazario, Xiangyao Yu, Kevin Chang, Rachata Ausavarungnirun, Onur Mutlu, "MinBD: Minimally-Buffered [8]. Deflection Routing for Energy-Efficient Interconnect", in SixthIEEE/ACM International Symposium on Networks on Chip (NoC), pp.1-10, May 2012.

- Robert Mullins, Andrew West, Simon Moore, "Low-Latency Virtual- Channel Routers for On-Chip Networks", *ISCA*, 2004. Cota E, Morais Antony, Soares Lubaszewski, "Reliability, Availability and Serviceability of Networks- on- Chip," *Springer*, 2010. [9].

- [10].

- [11]. Lin, B., Ramanujam, R.S.: Destination-based adaptive routing on 2D mesh networks. In: Proceedings of the International Conference on Architectures Networking and Communication Systems, pp. 1-12, October 2010

- Ma, S., Enright-Jerger, N., Wang, Z.: DBAR: An efficient routing algorithm to support multiple concurrent applications in [12]. Network-on-Chip. In: Proceedings of the International Symposium Computers and their Applications, pp. 413–424, June 2011

- [13]. Ramakrishna, M., Gratz, P., Sprintson, A.: GCA: Global congestion awareness for load balance in Network-on-Chip. In: Proceedings of the IEEE International Symposium NoC, Tempe, pp. 1–8, April 2013 Becker D., Dally, W.: Allocator implementations for Network-on-Chip routers. In: Proceedings of the International Conference on

- [14]. High Performance Computing Networking, Storage & Analysis, Portland, OR, pp. 1–12, November 2009

\_\_\_\_\_ IOSR Journal of Electronics and Communication Engineering (IOSR-JECE) is UGC approved Journal with Sl. No. 5016, Journal no. 49082.

\_\_\_\_\_

B.Nageshwar Rao. "An Improvised Quality Aware Adaptive Aware Routing for on chip based Wireless Network on Chip Communication." IOSR Journal of Electronics and Communication Engineering (IOSR-JECE), vol. 12, no. 5, 2017, pp. 01–05.

\_\_\_\_\_